1ère Année

# 7ème leçon : Le transistor à effet de champ à grille isolée : le MOSFET

- I. MOS à enrichissement

- Structure et symbole

- Comportement du MOSFET

- » Régime linéaire ou ohmique

- » Régime saturé ou transistor

- Courbes caractéristiques

- II. L'amplification avec un MOSFET.

- Schéma équivalent petits signaux

- III. MOS à appauvrissement

- IV. Portes logiques à transistors MOS

- NMOS

- CMOS

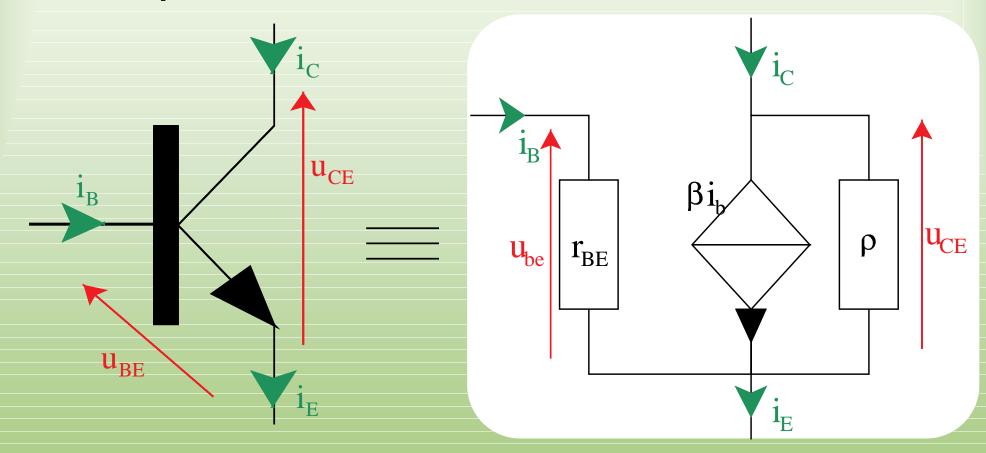

## Rappel n°1: Le bipolaire NPN

Générateur de courant commandé par un courant Diode passante en entrée

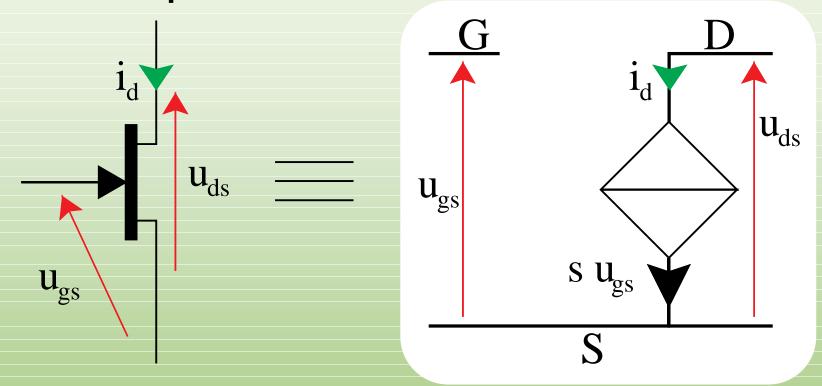

# Rappel n°2: Le JFET à canal N

Générateur de courant commandé par une tension Diode bloquée en entrée

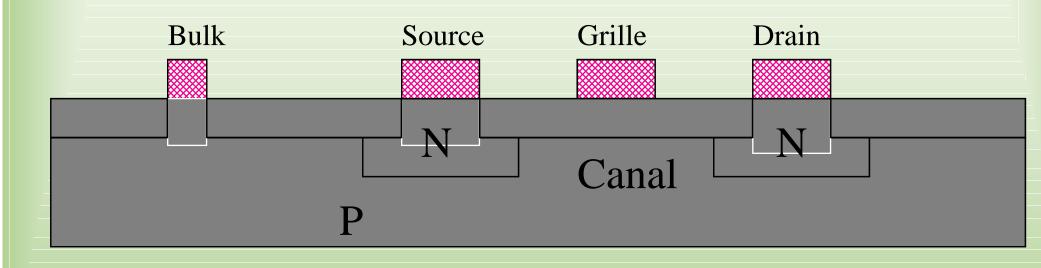

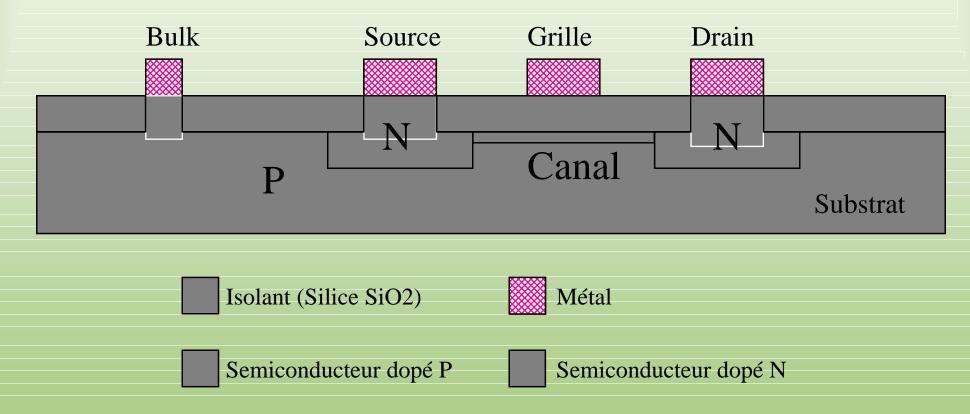

iD dépend de la géométrie du canal, modifiée par la zone de déplétion de la diode bloquée. Transistor MOS à enrichissement (Metal Oxide Semiconductor)

Structure en surface (planar) :

"facile" à fabriquer en grand nombre

Isolant (Silice SiO2) Métal

1ère Année

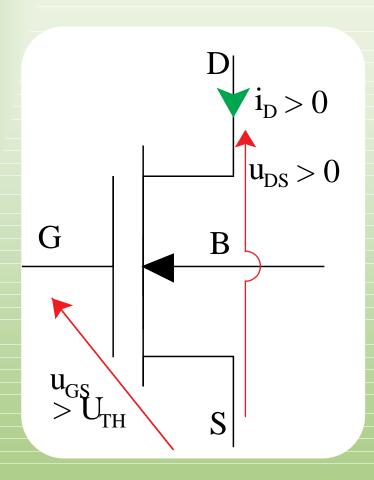

#### **Enrichissement (canal N)**

- Par défaut, une telle structure a une résistance infinie (RDS = 10 G $\Omega$ ). Si une tension est appliquée, uDS # 0, l'une des deux diodes substrat-source ou substrat-drain se bloque.

- Pourtant, si on applique une tension de grille ucs, le champ électrique créé sous la grille chasse les trous du substrat et attire les électrons.

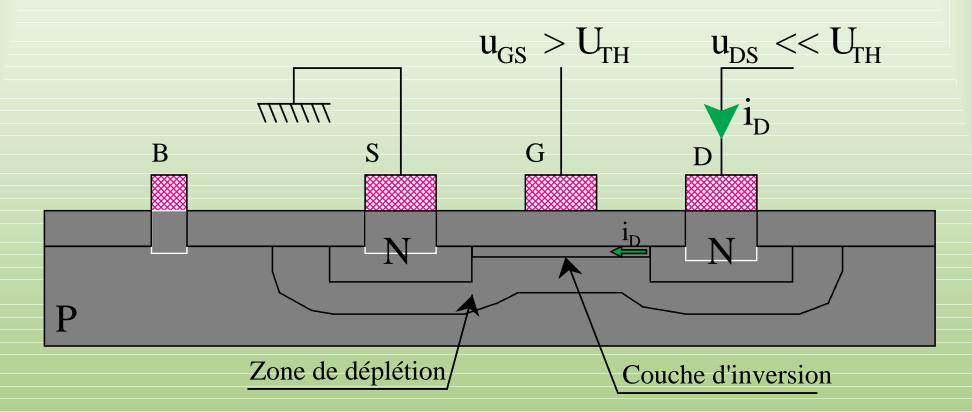

- Si ugs > Uth, la tension de seuil, une "couche d'inversion" se forme, qui constitue le canal, RDS diminue rapidement. Le canal se forme par "enrichissement" en électrons.

#### Régime Ohmique (résistance)

• Si ups n'est pas trop élevée, ups << Uтн, alors Rps dépend du nombre de porteurs dans le canal, attirés par ugs.

#### Résistance variable

• En régime ohmique, RDS diminue si ugs augmente

$$RDS = \frac{RDS0}{\frac{UGS}{UTH}}$$

et

$$|uGS| > |UTH|$$

RDS est quasi infinie si uGS ~ UTH

Remarque : la conductance du canal dépend linéairement de uGS.

$$GDS = GDS0 \left[ \frac{uGS}{UTH} - 1 \right]$$

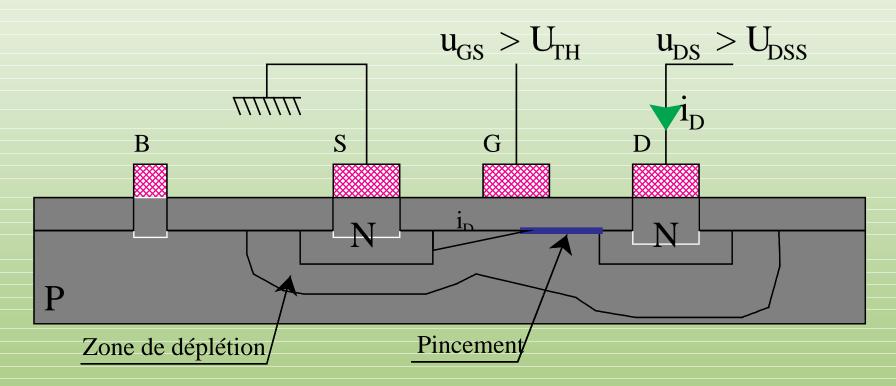

# Régime pincé (transistor)

- Si uns suffit à dépolariser une partie de la capacité M-O-S La couche d'inversion disparaît coté drain.

- Les porteurs franchissent l'obstacle par effet tunnel.

ugs contrôle directement le nombre de porteurs dans le canal (# JFET)

#### Le MOS comme transistor

Le nombre de porteurs du canal augmente avec uss, donc le courant de drain in aussi.

$$iD = IDSS \left( \left| \frac{uGS}{UTH} \right| - 1 \right)^2$$

avec |uDS| > |UTH|

et |uGS| > |UTH|

### Le "gain" du transistor MOS

La transconductance gm = s est la pente de id(uss) gm dépend du point de repos (ID, Uss)

$$g_{m} = s = \frac{\partial iD}{\partial u_{GS}} = \frac{id}{u_{gs}} = 2 \frac{\sqrt{ID \ IDSS}}{UTH}$$

Il est possible d'augmenter le gain en augmentant ID, le courant de drain au repos

iD(ugs) est une parabole, ce qui limite le domaine linéaire.

1ère Année

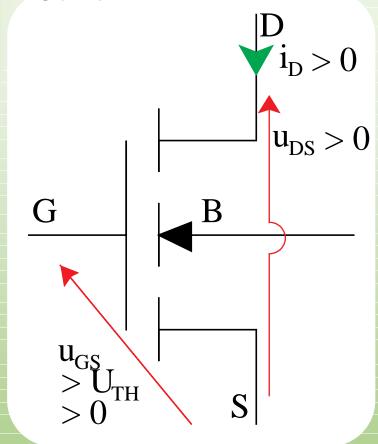

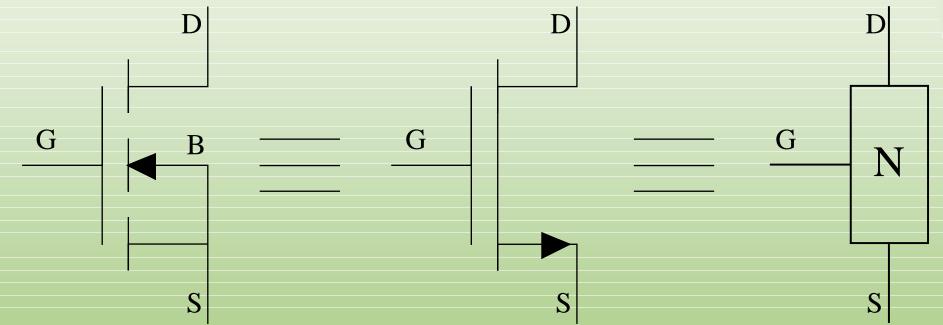

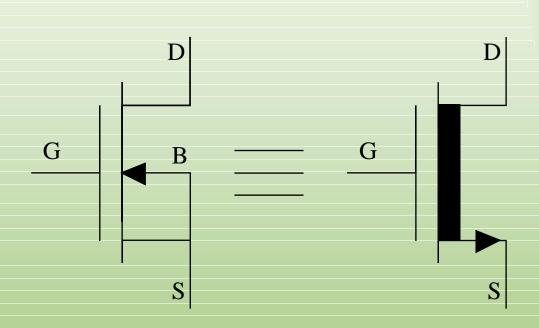

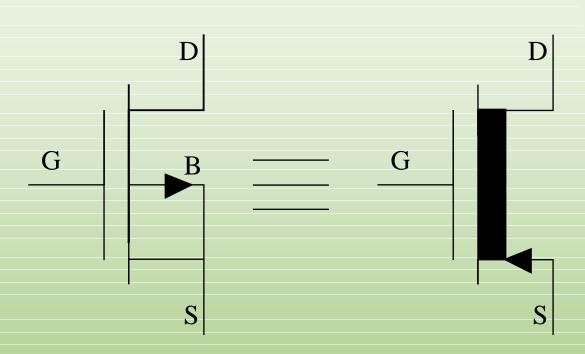

# Symboles des MOS à enrichissement (FET de type C)

Canal N

Canal P

La flèche indique le sens passant de la diode substrat-canal

# Symboles usuel du NMOS de type C

- 1er symbole : Le bulk est le plus souvent relié au drain

- Le 2ème symbole suppose le canal enrichi et pincé

- Le 3ème symbole, utilisé en logique, assimile le MOS à une résistance infinie (bloqué) ou faible (passant)

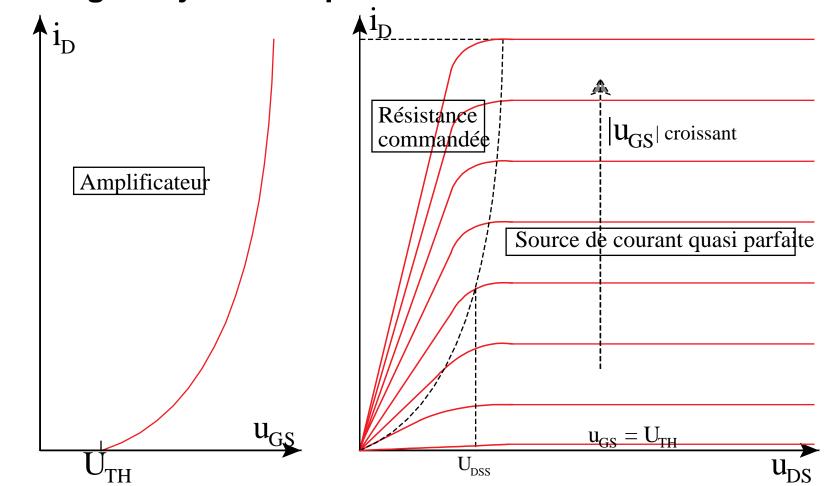

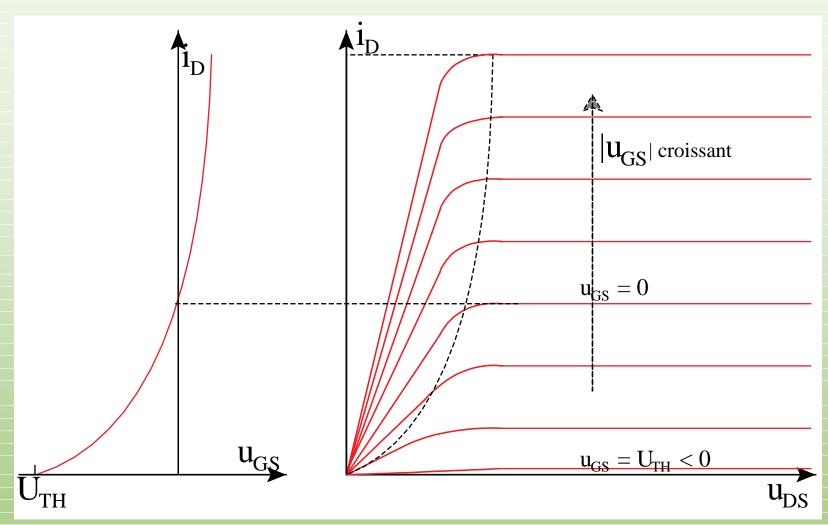

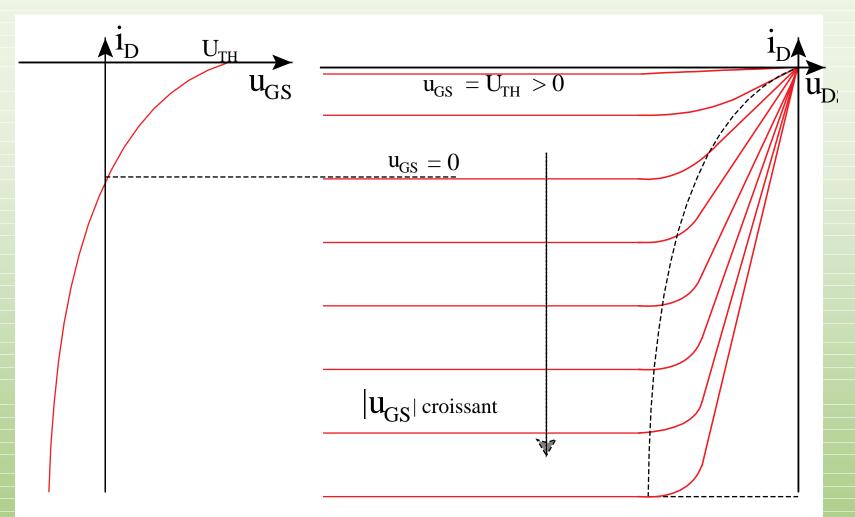

# Caractéristique du NMOS de type C

Avantage majeur : bloqué si uss = 0

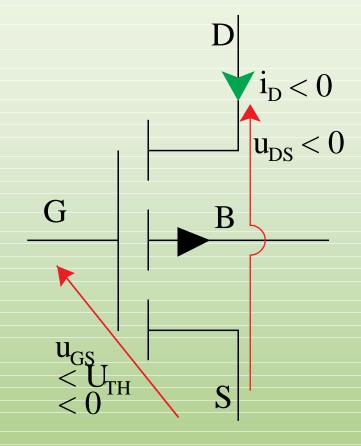

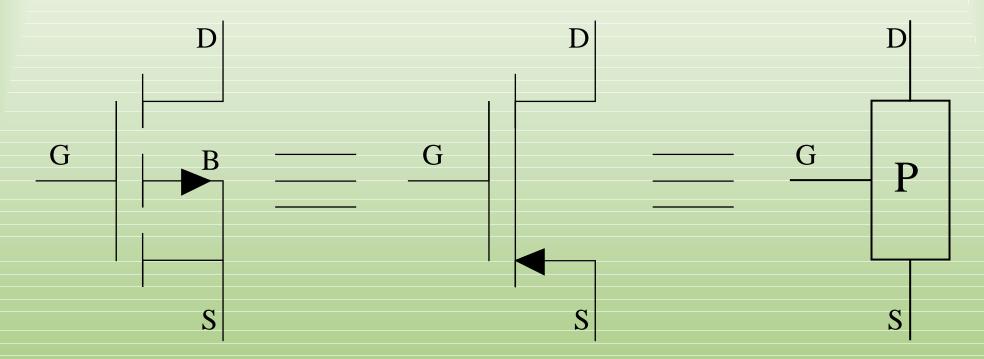

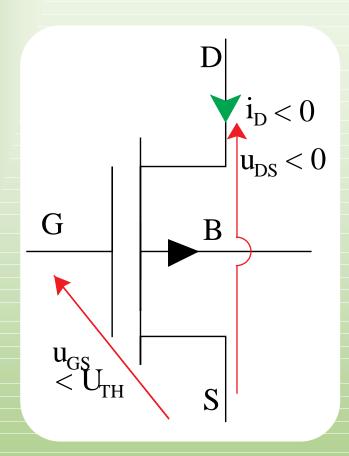

### Symboles usuel du PMOS de type C

- Même remarques que pour le NMOS :

- le plus souvent B = S et le canal est enrichi, pincé

- en logique, il est commode d'assimiler le MOS à une résistance

Toutes les variables (iD, uDS, uGS) sont négatives

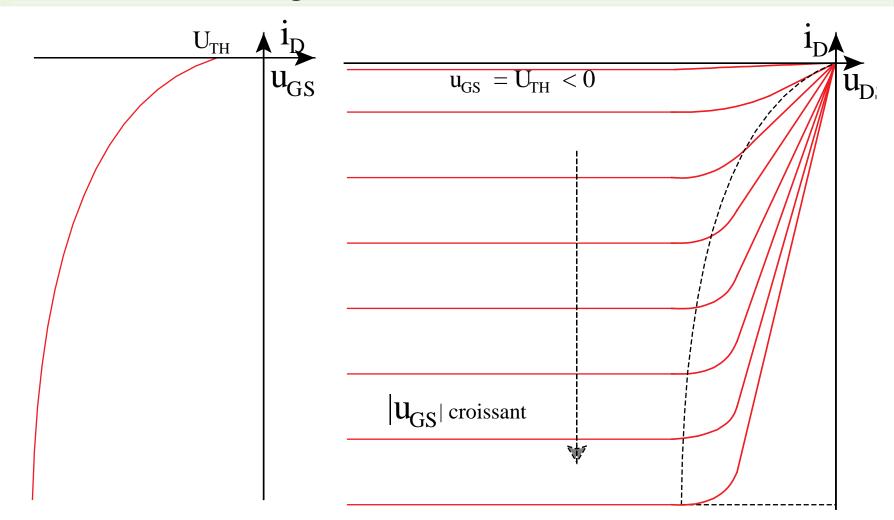

## Caractéristique du PMOS de type C

Les variables sont négatives

#### Utilisations des MOS à enrichissement

#### Interrupteur

C'est la principale utilisation des MOS. Si uDS > UTH :

uGS < UTH <=> MOS bloqué <=> iD ~ 0 (le blocage est

excellent)

uGS > UTH <=> MOS passant <=> iD = IDSS = cte

#### Amplificateur

La capacité de la grille limite la bande passante du système.

Les progrès actuels repoussent toujours plus loin ce défaut.

#### Résistance commandée

RDS est beaucoup plus grande dans un MOS que dans un JFET, aussi ce dernier sera souvent préféré pour cette application.

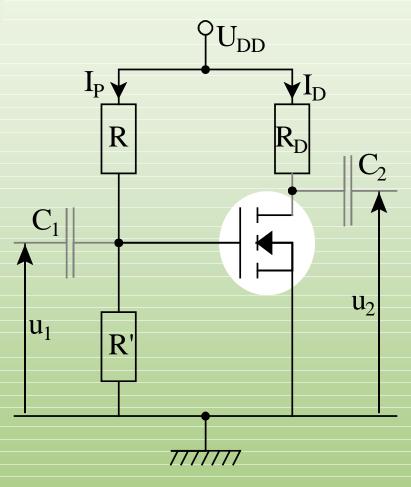

### Amplificateur à MOS

• Le montage à drain commun est le seul intéressant.

Le pont de grille est en sortie ouverte pour le continu. Il fixe UGS au niveau souhaité.

1ère Année

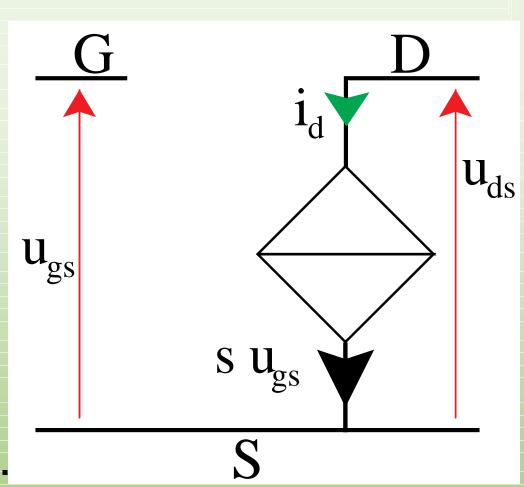

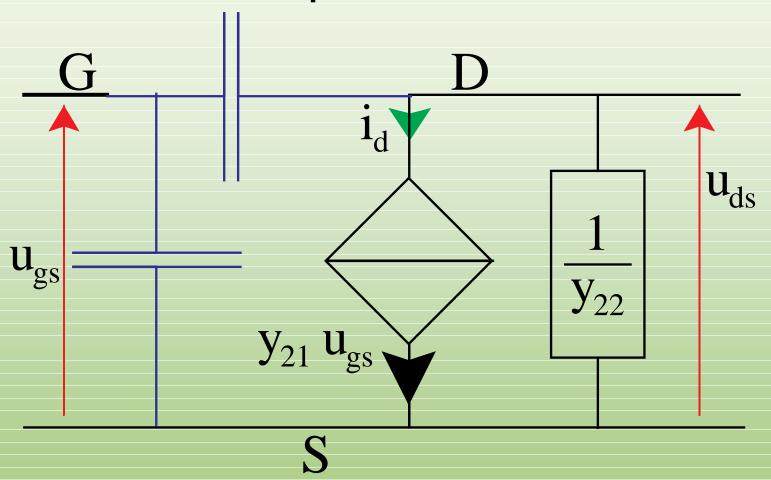

# Le schéma équivalent en petits signaux est le même pour tous les FET

- La capacité MOS est assimilable à un circuit ouvert en entrée.

- Les paramètres peuvent s'exprimer sous la forme d'une matrice y.

- iD augmente faiblement avec uds, ce qui peut être modélisé par une résistance de sortie en parallèle sur le générateur.

1ère Année

# A haute fréquence, le condensateur MOS reprend ses droits.

• Il faut alors en tenir compte.

# Le MOS à appauvrissement (FET de type B)

- Fonctionne sur le même principe qu'un type C Le canal est préimplanté à la fabrication

- Donc ce MOS conduit par défaut (ugp = 0)

## Symboles du NMOS à appauvrissement

Les symboles manifestent la continuité du canal à uGS = 0.

1ère Année

# Caractéristiques du NMOS à appauvrissement

### Symboles du PMOS à appauvrissement

1ère Année

# Caractéristiques du NMOS à appauvrissement

### Les portes logiques à base de MOS (C)

- L'immense majorité des transistors MOS est utilisée dans les circuits logiques à haute intégration (VLSI).

- Les avantages des MOS en logique sont nombreux :

- "Faciles" à intégrer à la surface des wafer

- Peuvent servir de résistors, de condensateurs ou d'interrupteurs

Il n'y a pas de composant ajouté dans une porte MOS

- Donc les portes MOS prennent moins de place que les TTL, à base de bipolaires

- L'impédance d'entrée très grande des MOS permet à une seule porte de commander beaucoup d'autres portes

- La moindre électricité statique détruit cette impédance

- Les porte CMOS (Coupled MOS) ne consomme pas de courant au repos

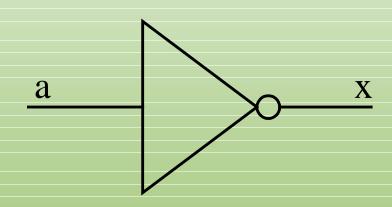

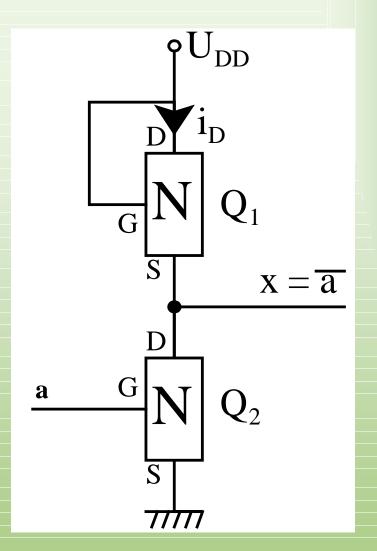

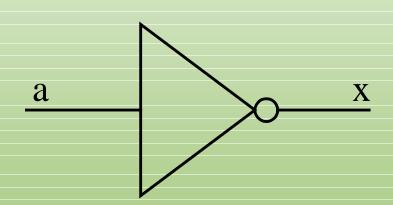

#### L'inverseur MOS

- Q1 est typiquement une "résistance"

UGS1 = UDD, donc Q1 est toujours passant

- Q1 et Q2 forment un pont diviseur dissymétrique.

- Par construction :

RQ1 passant >> RQ2 passant

et RQ1 passant << RQ2 bloqué</li>

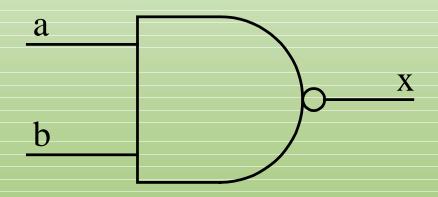

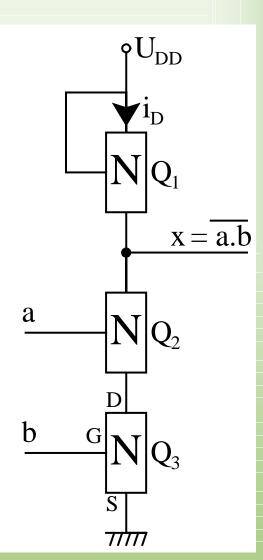

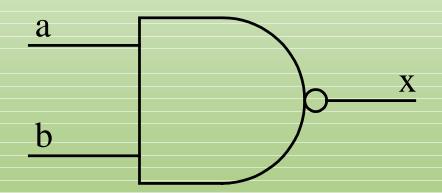

#### Le NAND MOS

- x = 0 si et seulement si a = b = 1

ux = 0 V si et seulement ua = ub = UDD

- Un 0 sur une borne correspond à un quasi- court-circuit de cette borne à la masse à travers un transistor passant

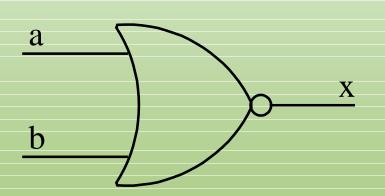

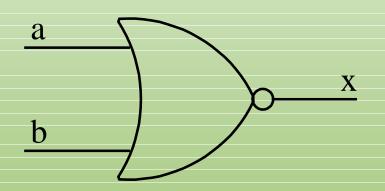

#### Le NOR MOS

- x = 1 si et seulement si a = b = 0

ux = UDD si et seulement ua = ub = 0 V

- Un 1 sur une borne correspond à un quasi-court-circuit de cette borne à l'alimentation.

#### L'inverseur CMOS

- Ici les géométrie des MOS sont identiques, mais leurs dopages opposés.

- Quelque soit ua (0 ou UDD) un des MOS est bloqué et l'autre passant

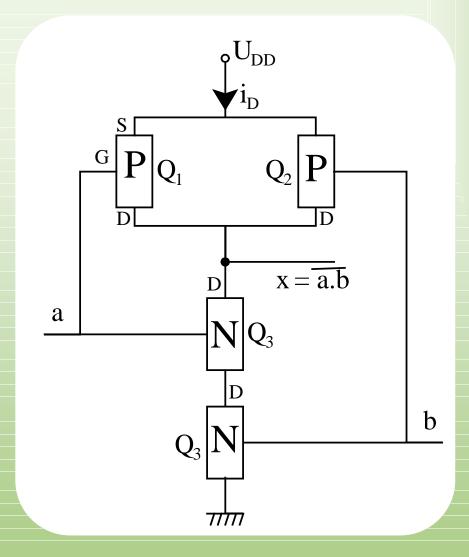

#### Le NAND CMOS

- La partie haute de la porte est bloquée ssi ua = ub = UDD.

- Dans ce cas, la partie basse est passant et ux = 0 V

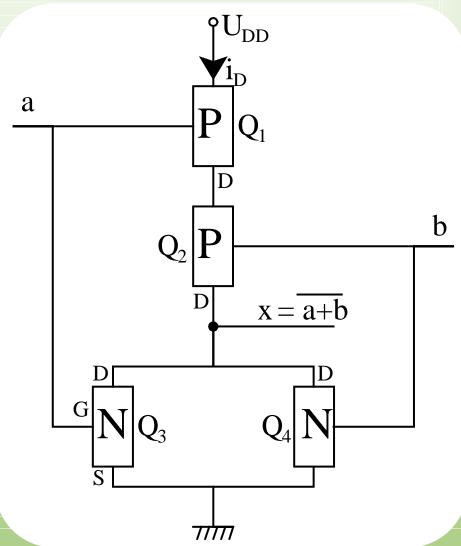

#### Le NOR CMOS

- La partie basse de la porte est bloquée ssi ua = ub = 0.

- Dans ce cas, la partie haute est passante et ux = UDD

## Avantages spécifiques des CMOS

- La tension d'alimentation peut être choisie entre 3 et 15 V

- La consommation de courant au repos est quasi-nulle

- Seul une commutation consomme du courant

- Donc l'augmentation de la fréquence d'horloge augmente la puissance dissipée

- Toutes les porte MOS ou CMOS sont très fragiles face à l'électricité statique (ou le erreurs de branchement). Une entrée de porte ne doit jamais être flotante.